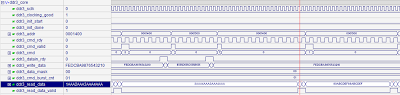

My initial simulation focus has been on DDR3. I chose DDR3 since it is the last hardware subsystem on Titan that has not been validated. I built a simple state machine that wrote data to two different addresses then read it back. From this simple test it looks like DDR3 is working. Figures 1-6 (below) show the simulation output. Figures 7-9 show the output from the Reveal Logic Analyzer on Titan.

I still need to take some measurements to validate that the signal integrity on the PCB is good, but for now it's good to know that the last subsystem on Titan (DDR3) is functioning.

|

| Figure 1. Write to Address 0x0001400 Marked (Data is 0x1AAA2AAAA3AAA4AAA Followed by 0xE555D555C555B555). |

|

| Figure 2. Write to Address 0x0001500 Marked (Data is 0x0123456789ABCDEF Followed by 0xFEDCBA987643210). |

|

| Figure 3. Read from 0x0001400 Marked Showing First Word (0x1AAA2AAAA3AAA4AAA). |

|

| Figure 4. Read from 0x0001400 Marked Showing Second Word (0xE555D555C555B555). |

|

| Figure 5. Read from 0x0001500 Marked Showing First Word (0x0123456789ABCDEF). |

|

| Figure 6. Read from 0x0001500 Marked Showing Second Word (0xFEDCBA9876543210). |

|

| Figure 7. Overall View Showing DDR3 Test in Hardware (Reveal Analyzer). |

| Figure 8. Close-Up View Showing DDR3 Data Read from 0x0001400 in Hardware (Reveal Analyzer). |

| Figure 9. Close-Up View Showing DDR3 Data Read from 0x0001500 in Hardware (Reveal Analyzer). |